by : Henry Toruan

Flip Flop adalah suatu rangkaian logika yang mempunyai sifat memori dimana outputnya selalu dipengaruhi oleh input-inputnya dan juga ditentukan oleh keadaan logika output sebelumnya.

RS-FLIP FLOP

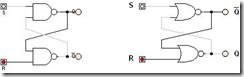

RS-FF adalah Reset Set Flip Flop yang merupakan rangkaian memori dasar dengan 2 output berlawanan Q dan . RS-FF dapat dibangun dengan NAND gate atau NOR gate seperti gambar berikut.

(a) (b)

Gambar Rangkaian RS-FF dengan NAND gate (a) dan NOR gate (b)

Hasil simulasi Rangkaian RS-FF menggunakan NAND gate dengan Digital Works :

Setelah mengamati pengaruh input R dan S terhadap output Q dan dan logic history, kita dapat menyusun tabel kebenaran suatu RS-FF.

Tabel kebenaran RS Flip Flop :

RS-FLIP FLOP CLOCKED

Fungsi pulsa untuk mengaktifkan FF sehingga diperoleh keadaan output yang sesuai dengan keadaan RS yang diberikan.

RS-FF clocked dapat dibangun dengan NAND gate atau NOR gate seperti gambar berikut.

(a) (b)

Gambar Rangkaian RS-FF clocked dengan NAND gate (a) dan NOR gate (b)

Hasil simulasi Rangkaian RS-FF menggunakan NAND gate dengan Digital Works :

Setelah mengamati pengaruh input R dan S terhadap output Q dan dan logic history, kita dapat menyusun tabel kebenaran suatu RS-FF clocked.

Tabel kebenaran RS Flip Flop clocked:

Keluaran RS-FF Clocked hanya berubah pada satu pulsa detak sehingga dikatakan FF beroperasi secara sinkron dimana FF ini beroperasi selangkah dengan detak.

Bila sekali diset atau direset maka akan tetap pada keadaan tersebut kecuali masukannya dirubah (karakteristik memori).

D-FLIP FLOP

D-FF adalah Data Flip Flop yang merupakan pengembangan RS-FF sering disebut flip-flop tunda data masukan D ditunda 1 pulsa detak dari pemasukan sampai keluaran Q. RS-FF dapat dibangun dengan NAND gate atau NOR gate seperti gambar berikut.

(a) (b)

Gambar Rangkaian D-FF dengan NAND gate (a) dan NOR gate (b)

Hasil simulasi Rangkaian D-FF menggunakan NAND gate dengan Digital Works :

Setelah mengamati pengaruh input R dan S terhadap output Q dan dan logic history, kita dapat menyusun tabel kebenaran suatu D Flip Flop.

Tabel kebenaran D Flip Flop:

Output D-FF akan selalu sama dengan inputnya bila mengalami transisi pulsa yang sesuai dengan FF yang bersangkutan.

D-FF dari NAND gate dan inverter akan aktif saat mengalami transisi pulsa positif, sedang D-FF dari NOR gate dan inverter akan aktif saat mengalami transisi pulsa negative.

D-FF dirangkai 1 sama lain untuk membentuk register geser dan register penyimpanan.

(74HC74, 74H273, 4013, 40174)

JK-FLIP FLOP

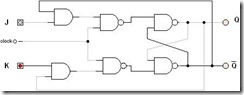

Input J dan K pada JK-FF mengontrol output FF dengan cara yang sama seperti S dan R dari RS-FF kecuali input J=K=1 tidak menghasilkan keadaan tak menentu tapi keadaan yang berlawanan dari sebelumnya bila terjadi transisi clock yang sesuai.

JK-FF clocked dapat dibangun dengan NAND gate dan AND gate seperti gambar berikut.

Gambar Rangkaian JK-FF dengan NAND gate dan AND

Hasil simulasi Rangkaian JK-FF menggunakan Digital Works :

Setelah mengamati pengaruh input J dan K terhadap output Q dan dan logic history, kita dapat menyusun tabel kebenaran suatu JK-FF.

Tabel kebenaran JK Flip Flop:

Tidak ada komentar:

Posting Komentar